¿Qué vamos a construir y para qué sirve?

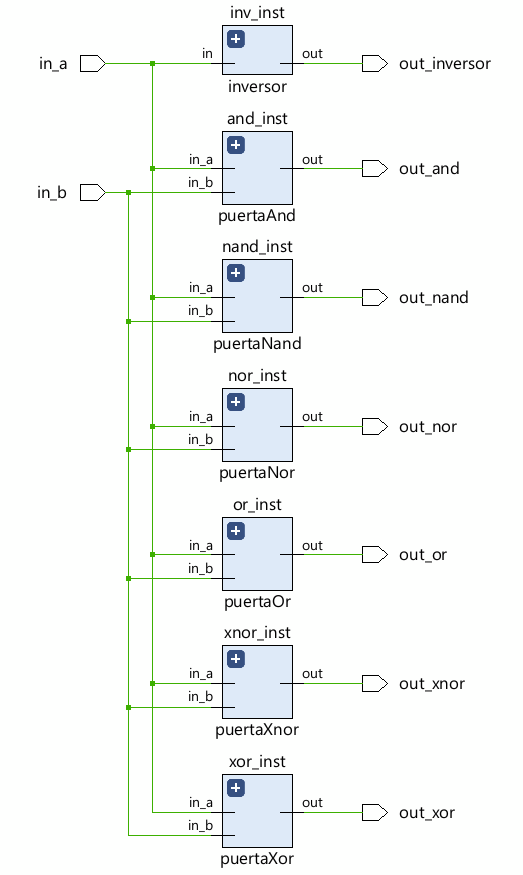

En este ejercicio se desarrolla un módulo de nivel superior llamado top_puertas, cuyo objetivo es integrar y coordinar varios submódulos de puertas lógicas básicas: NOT, AND, OR, NAND, NOR, XOR y XNOR.

El diseño utiliza dos señales de entrada (in_a e in_b) y genera una salida independiente para cada tipo de puerta lógica. Cada salida se conecta a un LED de la tarjeta Nexys A7-100T, permitiendo observar físicamente el comportamiento de cada operación lógica.

Este ejercicio introduce un cambio importante respecto a los anteriores:

ya no se diseña un único bloque, sino un sistema jerárquico compuesto por múltiples módulos reutilizables.

Conceptos clave que necesitas entender

Jerarquía en Verilog

En diseños reales, los sistemas digitales se construyen de forma jerárquica, combinando bloques pequeños y bien definidos para formar sistemas más grandes.

En este ejercicio:

- Cada puerta lógica se implementa como un módulo independiente

- El módulo

top_puertasinstancia y conecta estos submódulos - Las señales de entrada se comparten y las salidas se distribuyen hacia los LEDs

Este enfoque mejora la legibilidad, la escalabilidad y el mantenimiento del diseño.

Reutilización de módulos

Una de las grandes ventajas de Verilog es la reutilización de bloques.

Una vez definida una puerta lógica como módulo, puede instanciarse tantas veces como sea necesario sin duplicar código.

Este principio es fundamental en:

- Diseño digital profesional

- Desarrollo de IPs

- Arquitecturas complejas como procesadores o controladores

Conexión estructural

A diferencia de ejercicios anteriores, aquí el diseño se basa principalmente en descripción estructural, donde los módulos se conectan explícitamente mediante señales internas.

Esto acerca al estudiante a la forma en que se diseñan sistemas digitales a nivel industrial.

¿Dónde se usa esto en el mundo real?

El uso de jerarquía y módulos reutilizables es una práctica estándar en prácticamente todos los sistemas digitales:

- Diseño de bloques funcionales en ASIC y FPGA

- Bibliotecas de celdas lógicas

- Unidades aritméticas y lógicas (ALU)

- Sistemas de control y procesamiento digital

- Plataformas de hardware modular

Este ejercicio sienta las bases para comprender cómo se construyen sistemas complejos a partir de componentes simples.

Código del ejercicio en GitHub

El repositorio contiene todo lo necesario para implementar y verificar este ejercicio:

- Código fuente en Verilog HDL

- Testbench para simulación del sistema completo

- Archivo de restricciones

.xdcpara la tarjeta Nexys A7-100T

👉 Repositorio de ejercicios en Verilog HDL para FPGA (código Verilog + XDC + testbench):

Se recomienda simular el diseño completo antes de cargarlo en la FPGA y verificar que cada LED responda correctamente a las combinaciones de entrada.

Reto: genera tu propia versión con ayuda de IA

Para reforzar los conceptos de jerarquía y reutilización, intenta generar tu propia versión del diseño utilizando una herramienta de IA.

Prompt sugerido:

Actúa como un ingeniero experto en diseño digital con FPGA y Verilog HDL.

Diseña un sistema jerárquico en Verilog que instancie módulos independientes para las puertas lógicas NOT, AND, OR, NAND, NOR, XOR y XNOR.

Crea un módulo de nivel superior llamadotop_puertasque conecte dos entradas comunes y genere una salida para cada puerta, pensado para visualizar los resultados en LEDs de la tarjeta Nexys A7-100T.

Incluye un testbench para simular el diseño completo.

Al revisar el resultado, analiza:

- La claridad de la jerarquía

- La correcta conexión de señales

- La separación entre diseño y verificación