¿Qué vamos a construir y para qué sirve?

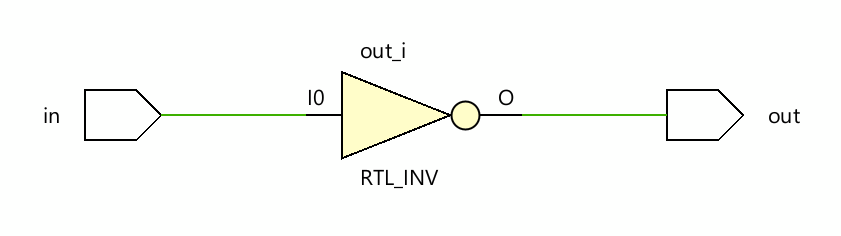

En este ejercicio se implementa un inversor lógico (NOT) en Verilog HDL, utilizando un solo interruptor de la tarjeta Nexys A7 como entrada (sw[0]) y un LED como salida (led[0]).

El comportamiento es simple:

cuando el interruptor está en 1, el LED se apaga;

cuando el interruptor está en 0, el LED se enciende.

Aunque funcionalmente trivial, este ejercicio marca un punto clave en la ruta de aprendizaje, ya que por primera vez se introduce el flujo completo de diseño digital:

- Descripción del módulo en Verilog

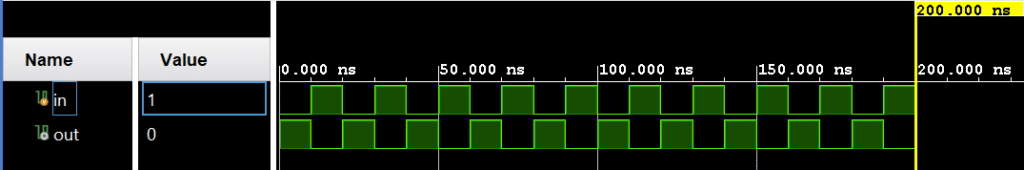

- Simulación del comportamiento mediante un testbench

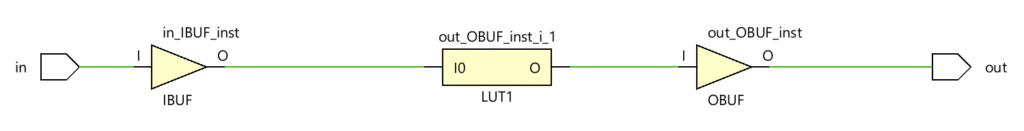

- Implementación en FPGA usando Vivado

- Asignación de pines mediante archivo .xdc

Este ejercicio conecta el código con la verificación y el hardware real.

Conceptos clave que necesitas entender

Inversión lógica

El inversor lógico es una de las puertas fundamentales del diseño digital. En Verilog, esta operación se expresa de forma directa utilizando el operador ~.

Separación entre diseño y verificación

A partir de este ejercicio aparece un nuevo concepto esencial:

el testbench.

- El módulo de diseño describe el hardware

- El testbench verifica su comportamiento

- El testbench no se sintetiza ni se implementa en la FPGA

Esta separación es una práctica estándar en diseño profesional de hardware digital.

Flujo de diseño digital

Con este ejercicio se introduce el flujo típico de trabajo:

- Escribir el módulo Verilog (RTL)

- Crear un testbench para simular el comportamiento

- Verificar que la salida sea correcta

- Implementar el diseño en la FPGA

- Asignar pines físicos usando el archivo

.xdc

Este flujo se repetirá, con mayor complejidad, en todos los ejercicios posteriores.

¿Dónde se usa esto en el mundo real?

La inversión lógica aparece constantemente en sistemas digitales reales:

- Señales activas en bajo (

active-low) - Botones y entradas con pull-up

- Reset de sistemas digitales

- Lógica de control e interbloqueos

- Interfaces industriales y automotrices

Comprender bien este concepto evita errores comunes cuando se trabaja con hardware real y señales físicas.

Código del ejercicio en GitHub

El código completo de este ejercicio está disponible en el repositorio, incluyendo:

- Módulo Verilog del inversor lógico

- Testbench para simulación

- Estructura compatible con Vivado

- Implementación pensada para la Nexys A7-100T

👉 Repositorio de ejercicios en Verilog HDL para FPGA:

Se recomienda simular el diseño antes de implementarlo en la FPGA y observar el comportamiento de la señal invertida en la simulación.

Reto: genera tu propia versión con ayuda de IA

Como ejercicio de refuerzo, intenta generar el diseño completo usando una herramienta de IA y luego compáralo con la solución del repositorio.

Prompt sugerido:

Actúa como un ingeniero experto en diseño digital con FPGA y Verilog HDL.

Diseña un módulo Verilog que implemente un inversor lógico usando un interruptor como entrada y un LED como salida para la tarjeta Nexys A7.

Incluye un testbench para simular el comportamiento del circuito y explica brevemente el flujo de diseño en Vivado, incluyendo la asignación de pines mediante un archivo .xdc.

Analiza especialmente:

- La diferencia entre el módulo y el testbench

- El uso correcto del operador de inversión

- La claridad del código y los comentarios